Broadcom Updates 802.11ac SoC Lineup with NAS-Friendly BCM5862x

by Ganesh T S on June 3, 2013 8:00 AM EST- Posted in

- Networking

- NAS

- Broadcom

- 802.11ac

- router

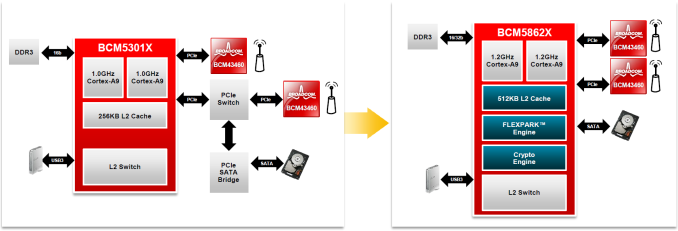

The initial batch of 802.11ac routers shipped with the dated and inefficient BCM4706 (based on a 600 MHz MIPS32 CPU). Broadcom made some amends last year with the BCM4708x / BCM5301x targeting the SOHO and SMB space respectively. Today, Broadcom is introducing the StrataGX BCM5862x to satisfy the market demand for SMB storage routers.

Broadcom has made some evolutionary updates to the BCM5301x in order to increase performance and simplify design.

The BCM5862x supports both 16 and 32b DDR3 (compared to the 16b-only BCM5301x). The Cortex-A9 cores gain an extra 200 MHz to run at 1.2 GHz. L2 cache is doubled from 256KB to 512KB. The SoC integrates two SATA ports (to accommodate such a design, the BCM5301x had to use an external PCIe switch and a PCIe SATA bridge). The Cortex-A9 cluster in the BCM5862x integrates NEON and VFP, as these features are important for NAS platforms. A 5-port GbE switch is also integrated. The FlexSPARX engine in the StrataGX BCM5862x provides packet and storage acceleration that offloads CPU for other tasks and a crypto engine provides support for IPsec / SSL and VPNs. These features make it attractive for integrated NAS / branch routers in SMB environments.

The StrataGX BCM5862x is available now and sampling to customers.

Source: Broadcom

8 Comments

View All Comments

DanNeely - Monday, June 3, 2013 - link

Is there any indication of how long before routers based on the new chip reach retail, and how much of a cost savings we can expect from the more integrated design?Kevin G - Monday, June 3, 2013 - link

I would have thought that they would have gone for 4 SATA ports + support for RAID5. Similarly, would have guessed an 8 port switch would have made more sense. The costs of adding these features can't be that much higher the 2 SATA and 5 port switch they have integrated. I guess shaving a few dollars in the design?DanNeely - Monday, June 3, 2013 - link

Market segmenting, or relative shares of the market perhaps? 5 ports is the standard in consumer routers (1 to the modem, 4 to the lan); and I suspect most consumer NASes sold are the smaller 1/2 drive models. Joe user doesn't need more storage than that, and a large fraction of consumers who do are geeks who'd lean towards building their own server to store the data anyway.Kevin G - Monday, June 3, 2013 - link

I get the market segmentation angle but I would have thought that it'd be wiser to go bigger and then fuse parts off or via binning create lower end SKU's. How much larger would the chip be if it supported 8 GbE ports instead of 5 GbE? Or two more SATA ports?DanNeely - Monday, June 3, 2013 - link

It'd depend how large the relative market shares are; if 95% of the sales are for the lower model it's a lot more wasteful than if only 50% are. If the chip size is being driven by the number of output pins not the amount of circuitry needed to drive the outputs the cost of adding more ports would be a lot larger than just the die area for extra controllers.Kevin G - Monday, June 3, 2013 - link

Margins also need to be considered. The more capable version can potentially get 5 times the margin for the same silicon with all the enterprise features enabled. So hypothetically 95% of the market is the low end models, the remaining 5% at the high end would drive 25% of the profits.The number of IO pins for the extra SATA ports and GbE ports are around 40-50 additional pins. There is a cost for adding those to the die as well as the package. Though for the more cost driven consumer parts, the package need not have those extra pins. I couldn't find package information on this chip but the previous generation BCM5300x are available in 400 and 484 pin BGA packages. Speaking of die size, that previous generation was also made on an older 65 nm process. Moving to 40/45 nm would easily allow inclusion of the extra logic for two SATA and three GbE ports. Going from an older MIPs based core to an ARM Cortex A9 would take up some die space afforded by a shrink but not all of it. Might as well go all-in with regards to IO when designing an SoC like this.

fteoath64 - Saturday, July 20, 2013 - link

I do not think a 1.2Ghz A9 DC can handle RAID 5 in software fast enough while doing all the other things it needs to do in the NAS itself. I would expect, this chip would have models scaling to 2Ghz and quadcore variants to handle SOHO NAS of 4 or 5 bays. It would give the Atom and low-end Haswell a run for its money. Also, it seems there is not much demand for 5 port switches, so 8 ports might be just a waste.zdw - Monday, June 3, 2013 - link

The nicest thing about this is that ARM generally is getting more attention from the software developers, whereas the MIPS platforms are pretty much dead ends aside from a few higher end vendors like Cavium, which ship in much lower volumes.Hopefully Broadcom will be more open with drivers for their chipsets - the 47xx series was known for having wireless driver issues that kept the *WRT projects back on ancient 2.4.x series Linux kernels for quite a while.