The Intel Xeon E7 v2 Review: Quad Socket, Up to 60 Cores/120 Threads

by Johan De Gelas on February 21, 2014 6:00 AM EST- Posted in

- IT Computing

- Intel

- Xeon

- Ivy Bridge EX

- server

- Brickland

The Core

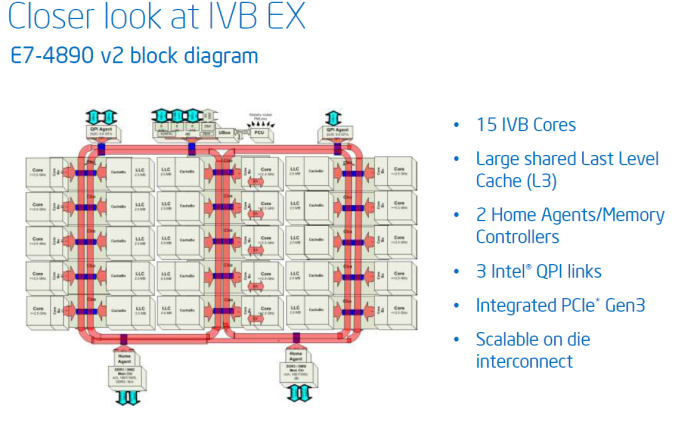

As Ian already discussed, the new Xeon E7 v2 is a 6, 8, 10, 12 or 15-core Ivy Bridge Xeon, similar to the Xeon E5-2600 v2. The big difference of course is that this new Xeon E7 v2 can be plugged into a quad- or native octal-socket server. These processors have three QuickPath Interconnects to be able to communicate over one hop. More sockets are possible with third party "glue logic".

Compared to the old Xeon E7 based on the "Westmere" core, the new Xeon E7 v2 "Ivy Bridge EX" features a vast amount of improvements. We will not list all of them, but just to give you an idea of how much progress has been made since the Westmere core:

- µop cache (less decoding)

- Improved branch prediction

- Deeper and larger OoO buffers

- Turbo Boost 2.0

- AVX instructions

- Divider is twice as fast

- MOVs take no execution slots

- Improved prefetchers

- Improved shift/rotate and split/load

- Better balance between Hyper-Threading and single-threaded performance; buffers are dynamically allocated to threads

- Faster memory controller

Most of the improvement were fine tuning but the combined effect of them should result in a tangible performance boost in integer performance. For software that uses AVX, the performance boost could be very substantial. Even in software that uses older SSE(2) code, we found that the Sandy Bridge/Ivy Bridge generations were 20% faster, clock for clock, and we should see similar results here.

The Uncore

Just like the Xeon E5-2600 v2, the Ivy Bridge EX cores and 2.5MB L3 cache slices are stacked in columns connected with three fast rings, which connect all cores and all other the units (called agents) on the SoC. These rings also make sure that the L3 slices can act as one unified 37.5MB L3 cache with 450GB/s of bandwidth. The latency to the L3 cache is very low: 15.5ns (at 2.8GHz) versus 20ns for Westmere-EX (Xeon E7-4780 at 2.4GHz). PCIe I/O now happens on the die as well, and each CPU can support 32 PCIe lanes.

Finally, some coherency improvements are also implemented. Modified cache lines are send straight to the requester, without any write back to the memory agent. Overall, the collective sum of the improvement should prove quite capable.

125 Comments

View All Comments

snoopy1710 - Friday, February 21, 2014 - link

Minor correction on the Dell E7-4890 SAP benchmark, which was done on SUSE Linux Enterprise Server for SAP Applications:http://download.sap.com/download.epd?context=40E2D...

Snoopy

FunBunny2 - Friday, February 21, 2014 - link

you should opt for ubuntu 12.04. "real" databases are approved only for LTS versions, and 12.04 is the latest.bji - Friday, February 21, 2014 - link

Page 10 does not contain the Linux Kernel Compile time benchmarks.JohanAnandtech - Saturday, February 22, 2014 - link

The web engine did something weird...I restored the pageJawsOfLife - Friday, February 21, 2014 - link

Very thorough review, which is what I've come to expect from Anandtech! I am interested but not very knowledgeable about the server side of computing, so this definitely filled me in on a lot of the facets of that area. Thanks for the writeup.By the way, the "Linux Kernel Compile" page is blank, as bji noted.

JohanAnandtech - Saturday, February 22, 2014 - link

Thx. A glitch in the engine made it delete a page. Restored.iwod - Friday, February 21, 2014 - link

While the revenue are high, just how many unit are shipped?I have been thinking if Intel would move Mobile First, meaning Atom, Tablet and Laptop Chips all gets the latest node first, which are low power design. While Desktop and Server will be a Architecture and Node behind. Which will align the Desktop and Xeon E3 - E5 Series.

But it seems the volume of Chips dont quite measure out, since the top end volume are far too small? Anyone have any idea on this.

dealcorn - Saturday, February 22, 2014 - link

I believe the statement "Still, that tiny amount of RISC servers represents about 50% of the server market revenues." should read "Still, that tiny amount of RISC servers represents about 50% of the high end server market revenues." Stated differently, from a revenue perspective Intel is #1 vendor in the high end segment even though it has less than a 50% market share. Server orders are placed with vendors, not architectures. Intel has fought an uphill battle to access the high end market and it is costly. However, if Intel can amortize its development costs over a larger revenue base than any competitor, it is well positioned to maintain it's share acquisition momentum.NikosD - Saturday, February 22, 2014 - link

@JohanVery nice review, I would like to see more benchmarks between E7 v2 vs RISC processors because I think the real competition is there.

Older Intel and AMD servers are not real competition for IvyBridge-EX.

It would be interesting when POWER8 is out, to give us the new figures of 8 socket benchmarks and if there is any progress on more 8+ sockets for Intel E7 v2 (built by Cray and other vendors)

I think that E7 v2 (I don't know about older vendors) can be placed in up to 32-socket systems - not natively of course.

JohanAnandtech - Saturday, February 22, 2014 - link

Older Intel systems are competition, because these kind of servers are not replaced quickly. If a new generation does not deliver substantial gains, some companies will postpone replacement. In fact, very few people that already have a quad intel consider the move to RISC platforms.But you have a point. But it is almost impossible for us to do an independent review of other vendors. I have never seen an independent review, and the systems are too scarce, so there is little chance that we can ask a friendly company to borrow us one.