Intel Discloses Lakefield CPUs Specifications: 64 Execution Units, up to 3.0 GHz, 7 W

by Dr. Ian Cutress on June 10, 2020 11:00 AM EST

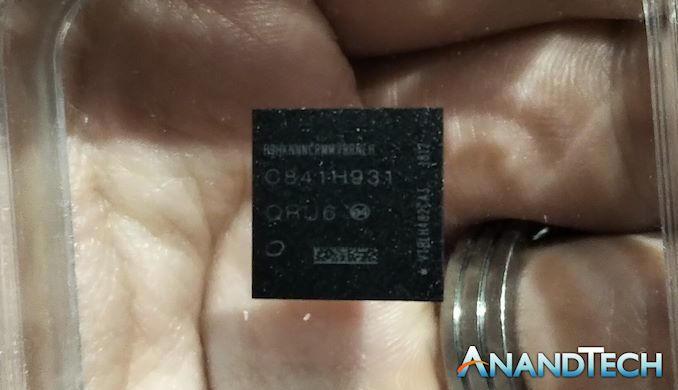

Over the past 12 months, Intel has slowly started to disclose information about its first hybrid x86 platform, Lakefield. This new processor combines one ‘big’ CPU core with four ‘small’ CPU cores, along with a hefty chunk of graphics, with Intel setting out to deliver a new computing form factor. Highlights for this processor include its small footprint, due to new 3D stacking ‘Foveros’ technology, as well as its low standby SoC power, as low as 2.5 mW, which Intel states is 91% lower than previous low power Intel processors. Today’s announcement comes in two parts: first, the specifications.

Intel will debut these two SKUs in its first generation of Lakefield. These CPUs will find homes in premium, always-connected laptops, such as the Samsung Galaxy Book S expected in markets this month, the Lenovo ThinkPad X1 Fold, coming later this year, and in the Microsoft Surface Book Neo.

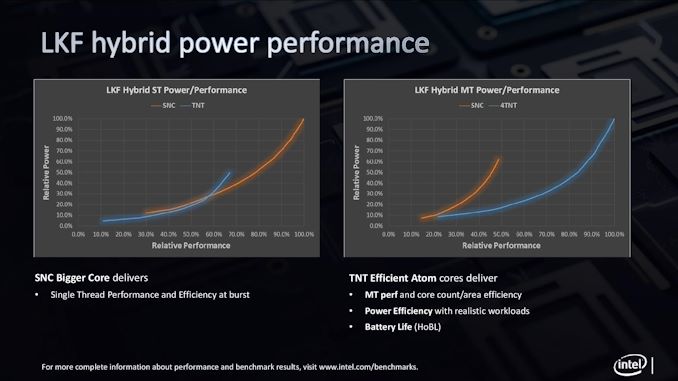

Both SKUs will feature one big ‘Sunny Cove’ CPU core, along with four little ‘Tremont’ Atom CPU cores. Both sets of cores will have access to a 4 MB last level cache, although Intel has not yet disclosed what sort of cache this is.

Meanwhile on the graphics front, Intel is integrating a Gen11 GPU with 64 execution units, the same number of EUs as on Intel's Ice Lake processors. Interestingly, the iGPU is clocked about half as high as usual for an Intel GPU, with clockspeeds peaking at just 500 MHz – suggesting that Intel is going wide and slow to increase graphics performance. Both CPUs will be rated for a TDP of 7 W.

| Intel Lakefield Processors | ||||||||

| AnandTech | Cores | Base Freq |

1C Turbo |

nT Turbo |

Gen11 IGP |

IGP Freq |

DRAM LP4 |

TDP |

| i5-L16G7 | 1+4 | 1400 | 3000 | 1800 | 64 EUs | 500 | 4267 | 7 W |

| i3-L13G4 | 1+4 | 800 | 2800 | 1300 | 48 EUs | 500 | 4267 | 7 W |

Intel confirmed to us that the base frequency is the unified frequency across all five cores, and the single core turbo frequency applies only to the big Sunny Cove core. Support for LPDDR4X-4266 is a notch above the memory controller in Ice Lake, which only runs at LPDDR4X-3733, and the memory speed will likely be a big boost to performance.

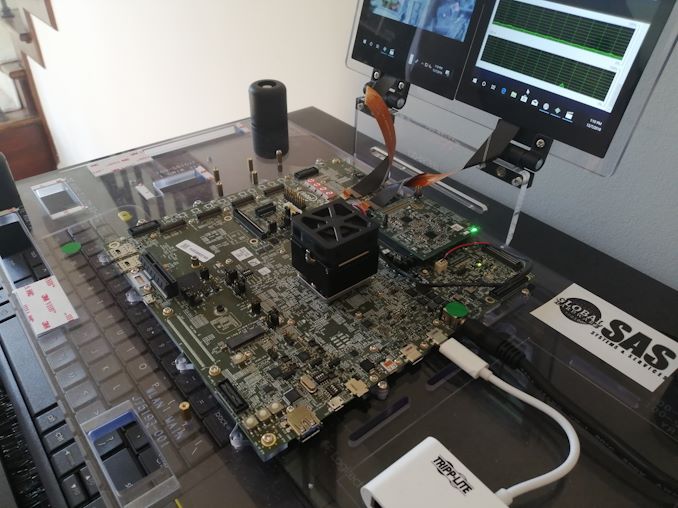

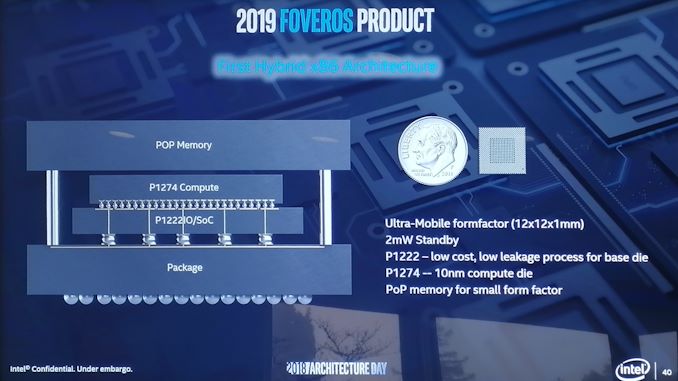

In order to enable these processors in a small 12mm x 12mm footprint, Intel is using its 3D stacking technology, called Foveros. This means that the logic areas of the chip, such as the cores and the graphics, sit on a 10+ nm die, while the IO parts of the chip are on a 22nm silicon die, and they are stacked together. In order to make the connections work, Intel has enabled 50 micron connection pads between the two silicon halves, along with power-focused TSVs (through silicon vias) in order to power the cores on the top layer.

Intel lists the TDP for these chips at 7 W, although the company has not disclosed the turbo power limits for the chip. As mentioned above, Intel hasn’t disclosed how the cache works. In the initial diagrams, we were shown that PoP memory would be added on top, and while Intel hasn't offered further details there, we know from last month's Samsung Galaxy Book S reveal that there will be (at least) 8GB SKUs using LPDDR4X.

We have big questions as to how each of the cores will work, given that by default they support different instruction sets – Intel hasn’t provided information on this at this time. Intel has stated that the scheduling of the threads on the different parts of the CPU will occur based on hardware-guided OS scheduling, although again Intel hasn’t gone into the details of its hardware tracking and enablement on how this is done. In the demos we have seen, Lakefield will use the Tremont cores for almost everything, and only call on the Sunny Cove core for user-experience type of interactions, such as typing or interacting with the screen.

Intel is planning a post-announcement briefing for press to ask questions, which means that this announcement is coming in two parts. This is the information we’re being given beforehand, and we will update you with the details from the post-announcement briefing. As part of this process, we’ve exclaimed to Intel how this way around of presenting details to the press is frustrating – firstly for readers, as you all will have to come back if you want to find out what more Intel tells us later today, but secondly for us, as press, who will have to scramble to jump on the details and decide whether to write fast and miss details, or write slow and miss the wave of traffic.

One thing we can confirm in advance – the Sunny Cove does not appear to be AVX-512 enabled. Intel’s initial press release states that AI workloads occur on the CPU; given the extra power draw required for AVX-512, this is probably a good thing.

More information out of Intel’s post-announcement press-briefing will come later today.

78 Comments

View All Comments

Spunjji - Tuesday, June 16, 2020 - link

It's a bit like AMD's APU dilemma - they need so much time to integrate the components on a working SoC that by the time it comes out, newer tech is already available (or close to becoming available).In this case that's magnified by them trying on a bunch of new manufacturing techniques for size.

JayNor - Wednesday, June 10, 2020 - link

gracemont+golden cove = alder lake, right?trivik12 - Wednesday, June 10, 2020 - link

That wont be low powered one. I am asking for something similar to this chip. So not so high clocked golden cove and 4 gracemont cores.JayNor - Wednesday, June 10, 2020 - link

Intel spokesperson stated there is an lte chiplet that can go into Lakefield's foveros stack.serendip - Wednesday, June 10, 2020 - link

This Intel big.little combo might be groundbreaking for Intel but it could end up like most other Atom-based efforts, stuck in niche markets with no mainstream traction even after billions of dollars being spent. Lakefield isn't competing against Atom or Ice Lake chips. It's going up against the Snapdragon 7cx/8cx with higher core counts and built-in LTE. The software situation for Linux and Windows on ARM is improving greatly and who knows, MacOS could join the fray too.Jon Tseng - Thursday, June 11, 2020 - link

TBH I think since early cherry trail, atom has really been aimed more at embedded markets like comm equipment (analogous to how Tegra is more an auto thing nowadays than a consumer part). Whatever consumer parts have come out have been more of an afterthought...serendip - Thursday, June 11, 2020 - link

Cherry Trail was supposed to get an upgrade to Willow Trail to be an LTE-capable tablet SoC but that was cancelled. Apollo Lake took its place and that's mainly aimed at servers, embedded and automotive. I've seen Apollo Lake laptops by low end Chinese manufacturers but they're rare and battery life isn't great, probably because of the higher TDP. Intel's loss with Atom is a net gain for ARM licensees.Deicidium369 - Friday, June 12, 2020 - link

The Nintendo Switch is built on Tegra X1 - quite consumer - but yeah outside of that - mostly autoSpunjji - Tuesday, June 16, 2020 - link

I feel like this is a pretty concerted attempt to get Atom back where they wanted it in the first place. It's certainly not looking like an embedded-first proposition.I guess we'll see whether or not it catches on, though.

69369369 - Thursday, June 11, 2020 - link

https://ark.intel.com/content/www/us/en/ark/produc...AVX/AVX2 not supported, 8GBs of memory max

Lame asf