PCIe 6.0 Specification Hits Version 0.5: On Track for 2021

by Anton Shilov on February 21, 2020 10:00 AM EST- Posted in

- Interconnect

- PCIe

- PCI-SIG

- PCIe 6.0

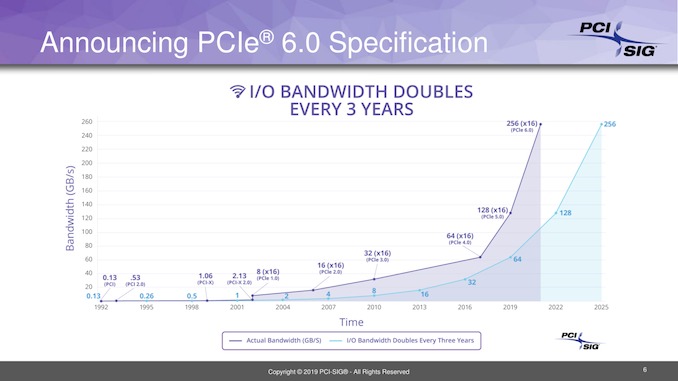

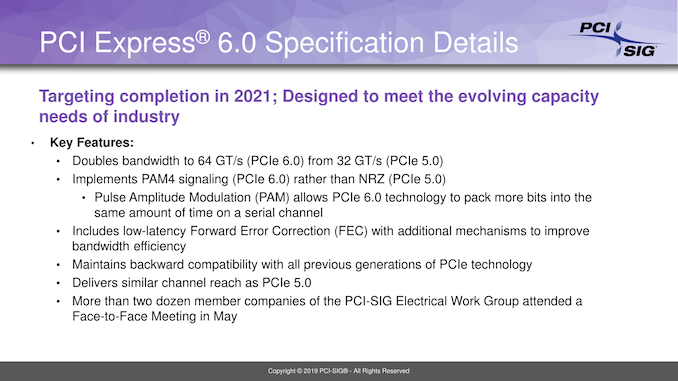

PCI-SIG has released version 0.5 of the PCIe 6.0 specification to its members this week. The new, "first draft" version of the spec includes the feedback the group got from its members after publication of version 0.3 back in October. With their latest update, PCI-SIG remains confident that it is on track to finalize the PCIe 6.0 standard in 2021.

It took PCI-SIG long seven years to complete the PCIe 4.0 specification, a long slog that the group has committed to avoiding going forward for PCIe 5.0 and beyond. With PCIe 6.0, PCI-SIG is keeping up that rapid pace of development, releasing the first draft version of the spec less than a year after formal announcement of the spec.

Overall, PCI-SIG has five key steps in creating a PCIe specification:

- Version 0.3 is beheld as a Concept and outlines the key features and architecture of the technology. In case of PCIe 6.0, we are talking about 64 GT/s per lane speed, pulse amplitude modulation with 4 levels (PAM-4) encoding, and forward error correction (FEC).

- Version 0.5 is considered as the First Draft specification and so it covers all the key aspects of the architecture and includes feedback from interested parties (within PCI-SIG) to version 0.3. Members of the group will be able to add new functionality to the technology at this point.

- Version 0.7 is deemed to be the Complete Draft, everything has to be defined at all levels and electrical specifications must have been validated via test chips. No new features may be added after release of this iteration of the specification.

- Version 0.9 is the Final Draft that is meant to allow PCI-SIG members to review the technology for their intellectual property.

- Version 1.0 is the Final Release.

The publication of version 0.5 of the PCIe 6.0 specification is essentially the final call for submissions of the new features by PCI-SIG member companies. Furthermore, with the first draft available, companies can start designing test silicon to ensure that everything works and even begin preliminary work on commercial chips.

The next milestone for the PCIe 6.0 specification will be the upcoming PCI-SIG Developers Conference 2020 in early June, where the group plans to present deep dives into the features of the technology.

Related Reading:

- PCIe 6.0 Dev Reaches v0.3; On-Track for a Full Specification In 2021

- PCI Express Bandwidth to Be Doubled Again: PCIe 6.0 Announced, Spec to Land in 2021

- Gen-Z PHY Specification 1.1 Published: Adds PCIe 5.0, Gen-Z 50G Fabric

- PCI-SIG Finalizes PCIe 5.0 Specification: x16 Slots to Reach 64GB/sec

- Synopsys Demonstrates CXL and CCIX 1.1 over PCIe 5.0: Next-Gen In Action

Source: PCI-SIG

74 Comments

View All Comments

RogerAndOut - Friday, February 21, 2020 - link

A lot of people are saying that there is no need for more than PCI 4.0 on the desktop - They are forgetting that for AMD PCI is the interconnect between chiplets - I/O die and the I/O die and the Southbridge chip. If AMD needs additional bandwidth on these connections it can change the PCI version and the desktop may just gain faster PCI slots.Brane2 - Friday, February 21, 2020 - link

Not true. There are different rules for internal, on the chip interconnect and PCIe lanes which have to mantain signal integrity relativelly far off-the chip and possibly even on cable.IF link between chiplets can be less than an inch long, on much higher quality substrate, smaller geometries ( ie silver or even gold traces between chiplets) and tightly equalized path lengts.

Also, microvia is "cheaper" than a full I/O pad, so the busses can be wider AND faster...

brunis.dk - Saturday, February 22, 2020 - link

So, Intel is still in 2010? ..back2future - Monday, December 20, 2021 - link

considering SSDs power requirements estimation for PCIe 5.0 (TDP <14W) and 6.0 (up to 28W) https://www.tweaktown.com/news/82402/phison-talks-...